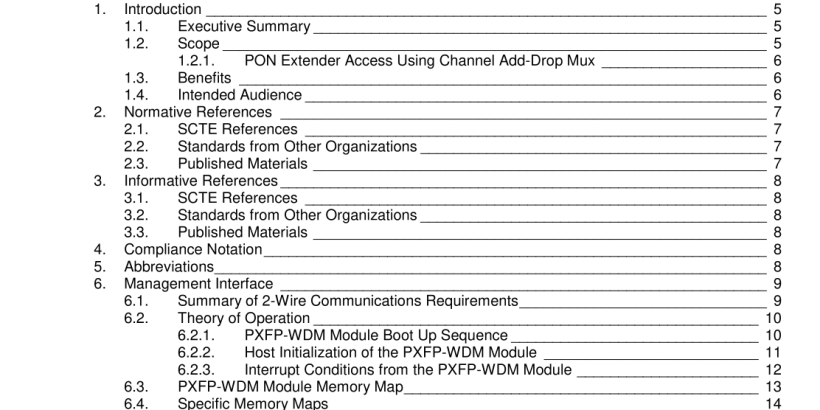

ANSI SCTE 233-2016 pdf download.Wavelength-Division Multiplex Small Form Factor Pluggable (PXFP- WDM) Optical Transmitter Module Interface Specification

6. Management

Interface 2-Wire Communications (I²C) for the PXFP-WDM module are based upon [XFP MSA]. I²C is an implementation of the NXP (formerly Philips) I²C [UM10204] specification with mapped memory address locations (also known as “well-known addresses”) for diagnostics and operations. The SFF Committee specifies the I²C common memory mapping in [XFP MSA] and [SFF-8477] for SFP and XFP, as well as additional physical layer requirements. This specification uses the same well-known memory map locations (addresses) for functions that are the same or substantially similar. Some memory map fields from [XFP MSA] and [SFF-8477] are re-allocated or not used; in addition, some memory map fields have been added. The PXFP-WDM module shall implement the I 2 C requirements specified in [XFP MSA], except where specified differently in the following sections.

6.2. Theory of Operation

Using Chapter 5: Management Interface of [XFP MSA] as reference, the following sections define the operation of the PXFP-WDM module I²C interface that is used for serial ID, digital diagnostics and other control/monitoring functions.

6.2.1. PXFP-WDM Module Boot Up Sequence

When a PXFP-WDM module is plugged in, the host needs to perform a number of initialization steps in a particular order with a particular timing. Some of these involve the PXFP-WDM module pins and some involve I²C communications. As most of these are documented in the [XFP MSA] or are implied by stated dependencies, a reference to the location(s) in that document will accompany each step in the following sequence descriptions. Before the boot up sequence can be discussed, communications and host requirements need to be understood.

In order to alert the host system to any condition outside of normal operating conditions, the PXFP-WDM module implements an Interrupt bit in byte 110; when the Interrupt bit is set, the host checks the alarm and warning flags to determine the condition. The host is required to periodically check the state of the Interrupt bit.

Existence of any of these conditions shall lead to a latched flag. These flags are located in bytes 80 – 87 and are detailed in Table 39 of [XFP MSA]. The presence of any 1 value in bytes 80 – 87 without a corresponding mask bit set to 1 will assert the Interrupt bit in byte 110.The host may query the latched flag bits in bytes 80 – 87. The PXFP-WDM module shall clear the latched flags upon the read of the corresponding latched flag bit. Masking bits shall be volatile and startup with all unmasked (masking bits 0). The mask bits can be used to prevent continued interruption from ongoing conditions. This specification uses byte 93, bit 0 for the vendor-specific alarm mask.

6.3. PXFP-WDM Module Memory Map

The structure of the PXFP-WDM module memory map is shown in Figure 5. The PXFP-WDM module shall implement the memory map specified in section 5 of [XFP MSA] and section 4 of [SFF-8477], with the exceptions specified here. The normal 256 byte I²C address is divided into lower and upper blocks of 128 bytes. The lower block of 128 bytes is always directly available and is intended to be used for diagnostic and control functions that are accessed often. This is the common table; it is accessed if the I²C address is less than 128 without regard to the selected table. Multiple blocks of memory are available in the upper 128 bytes of the address space. These are individually addressed via a table select byte located in the lower address space (at offset 127). The upper address tables are intended to contain information that is accessed less frequently, such as serial ID, user writable EEPROM, etc. The password must be entered before any upper memory can be accessed. The password entry stays in effect until the module is power cycled. Figure 5 summarizes the memory layout. The major difference from [XFP MSA] is that some fields are not supported or used differently, as detailed in section 6.4.2.ANSI SCTE 233-2016 pdf download